## THÈSE DE DOCTORAT

**SPECIALITE: PHYSIQUE**

Ecole Doctorale « Sciences et Technologies de l'Information des Télécommunications et des Systèmes »

Présentée par :

### Alexandre GUERRE

Sujet:

# Approche hiérarchique pour la gestion dynamique des tâches et des communications dans les architectures massivement parallèles programmables

Soutenue le ...24 septembre 2010 .....devant les membres du jury :

M.Lavenier Dominique, Rapporteur, DR CNRS, IRISA

M.Torres Lionel, Rapporteur, Professeur, Université de Montpellier 2

M.Auguin Michel, Examinateur, DR CNRS, Université de Nice-Sophia Antipolis

M.Gogniat Guy, Examinateur, Université de Bretagne Sud

M.Mérigot Alain, Directeur, Professeur, Université Paris Sud

M.David Raphaël, Co-directeur, Ingénieur Chercheur au CEA LIST

M. Ventroux Nicolas, Co-directeur, Ingénieur Chercheur au CEA LIST

Computers are useless. They can only give you answers. par Pablo Picasso (1881 - 1973)

# Remerciements

J'ai réalisé mes travaux de thèse au sein du Laboratoire Calcul Embarqué (LCE) du Laboratoire d'Intégration des Systèmes et des Technologies (LIST) au Commissariat à l'Energie Atomique et aux Energies Alternatives (CEA) de Saclay. C'est pourquoi je voudrais remercier Laurent Letellier et Raphaël David de m'avoir accueilli au sein du Laboratoire et de m'avoir permis de mener à son terme ma thèse dans les meilleures conditions.

Je remercie Alain Mérigot, professeur à l'Institut d'Electronique Fondamental (IEF) de l'université Paris Sud, de m'avoir fait l'honneur d'encadrer ma thèse et pour ses conseils avisés durant ma thèse.

J'adresse mes remerciements sincères à Nicolas Ventroux, ingénieur chercheur, et Raphaël David, chef du Laboratoire, pour m'avoir encadré et conseillé tout au long de ces trois années. Je tiens à les remercier plus particulièrement pour leur patience et leur soutien durant ma thèse et enfin pour m'avoir offert l'opportunité de continuer ma démarche de recherche au CEA.

Je remercie Michel Auguin, directeur de recherche CNRS à l'université de Nice-Sophia Antipolis, d'avoir accepté de présider mon jury de thèse.

Je remercie également Dominique Lavenier, directeur de recherche CNRS à l'IRISA, et Lionel Torres professeur à l'université de Montpellier 2, d'avoir accepté de juger mon travail en tant que rapporteurs.

Je tiens à remercier Guy Gogniat, professeur à l'université de Bretagne Sud pour sa participation à mon jury de thèse.

Je tiens également à remercier Tanguy Sassolas, Maroun Ojail, Jean-Marc Philippe et Pierre Guironnet de Massas pour le temps qu'ils ont consacré à relire ma thèse ainsi que pour leurs remarques pertientes.

Je remercie l'ensemble des membres du Laboratoire LCE pour leur aide durant ma thèse mais aussi pour la bonne humeur régnant dans le laboratoire. J'aimerais aussi remercier l'ensemble des participants de nos pauses thé pour nos nombreux fous rires.

Je remercie Julien, Pablo et le laboratoire LFSE pour m'avoir si bien accueilli lors de mon passage au bâtiment 451.

Je remercie également Tof et Marina et tous mes amis d'école (Bérichon, Joker, JJ, Ben et Camille) qui m'ont soutenu et encouragé durant ma thèse ainsi que pour les bons moments passés avec eux.

Je tiens à remercier les membres de l'association MAIOT pour avoir supporté humour et de m'avoir permis de passer de très bons moments tout au long de ma thèse. Je tiens à remercier plus particulièrement Véronique, Agnès, Julien, Benoit, Clémence, Sophie, Laura, Sarah, Aurélie et tous les autres avec qui j'ai passées de bonnes soirées.

Je voudrais terminer ces remerciements par un grand merci à mes parents et à mon frère pour leur aide et leurs encouragements dans les moments durs.

# Table des matières

|   | Intr           | $\mathbf{roduct}$ | ion                                                                | 1  |

|---|----------------|-------------------|--------------------------------------------------------------------|----|

|   |                | Conte             | exte de l'étude                                                    | 1  |

|   |                | Plan o            | du manuscrit                                                       | 4  |

| 1 | Eta            | t de l'           | art                                                                | 7  |

|   | 1.1            | Les ar            | rchitectures multiprocesseurs existantes                           | 8  |

|   |                | 1.1.1             | Les solutions statiques                                            | 9  |

|   |                | 1.1.2             | Les solutions dynamiques                                           | 10 |

|   |                | 1.1.3             | Conclusion sur les architectures multiprocesseurs                  | 11 |

|   | 1.2            | Choix             | d'un type d'interconnexion                                         | 12 |

|   |                | 1.2.1             | Connexion point à point                                            | 12 |

|   |                | 1.2.2             | Connexion par bus                                                  | 13 |

|   |                | 1.2.3             | Réseaux sur puce : NoC (Network on Chip)                           | 14 |

|   |                | 1.2.4             | Synthèse sur les modes de communication                            | 16 |

|   | 1.3            | Les ca            | aractéristiques des réseaux sur puce                               | 17 |

|   |                | 1.3.1             | L'étude théorique des réseaux sur puce                             | 17 |

|   |                | 1.3.2             | Les éléments de base des NoC                                       | 18 |

|   |                | 1.3.3             | Les mécanismes de transport                                        | 19 |

|   |                | 1.3.4             | La topologie                                                       | 21 |

|   |                | 1.3.5             | Les algorithmes de routage                                         | 26 |

|   |                | 1.3.6             | Le contrôle de flux                                                | 27 |

|   |                | 1.3.7             | Qualité de service (Quality of Service : QoS)                      | 29 |

|   | 1.4            | Concl             | usions de l'état de l'art                                          | 30 |

| 2 | Mis            | e en p            | lace d'un environnement de simulation pour l'exploration           |    |

|   | $\mathbf{des}$ | réseau            | ıx sur puce                                                        | 33 |

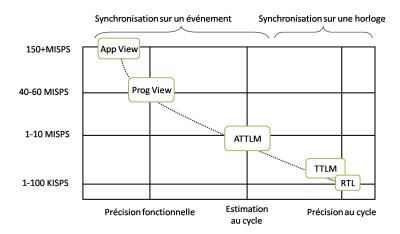

|   | 2.1            | Choix             | du niveau de simulation                                            | 34 |

|   | 2.2            | Etat o            | de l'art des simulateurs de réseaux sur puce                       | 36 |

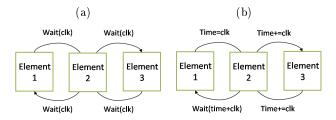

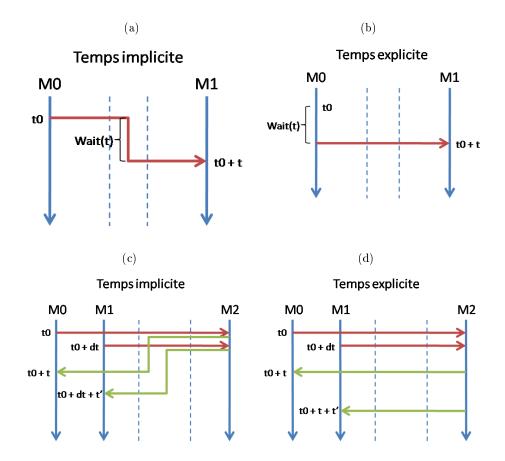

|   | 2.3            | Timed             | d TLM contre Approximate-Timed TLM                                 | 38 |

|   | 2.4            | Descr             | iption de notre structure de simulation                            | 40 |

|   |                | 2.4.1             | Implantation des réseaux sur puce                                  | 40 |

|   |                | 2.4.2             | Un environnement de simulation pour la comparaison de to-          |    |

|   |                |                   | pologies                                                           | 46 |

|   | 2.5            | Carac             | térisation de la rapidité et de la précision de notre simulateur . | 48 |

|   |                | 2.5.1             | Caractérisation de la rapidité                                     | 49 |

|   |                | 2.5.2             | Caractérisation de la précision                                    | 50 |

|   | 2.6            | Concl             | usion sur la nouvelle approche proposée                            | 51 |

| <b>3</b> | $\mathbf{Pro}$ | positio | on d'une topologie hiérarchique indépendante de l'appli-                            |            |

|----------|----------------|---------|-------------------------------------------------------------------------------------|------------|

|          | cati           | f et ef | ficace d'un point de vue silicium                                                   | <b>5</b> 3 |

|          | 3.1            | Descri  | ption de réseaux représentatifs de l'espace de conception et leur                   |            |

|          |                | impléı  | mentation dans le simulateur                                                        | 54         |

|          |                | 3.1.1   | Les réseaux à plat                                                                  | 55         |

|          |                | 3.1.2   | Les réseaux hiérarchisés                                                            | 56         |

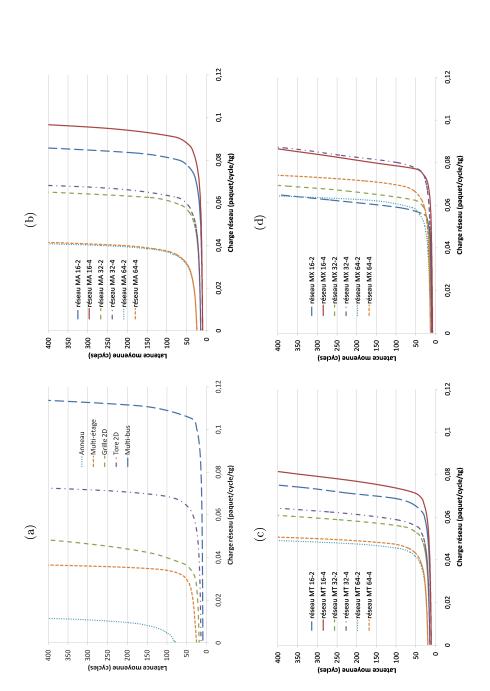

|          | 3.2            | Comp    | araison des performances des différentes topologies                                 | 59         |

|          |                | 3.2.1   | Comparaison des performances sous trafic uniforme                                   | 59         |

|          |                | 3.2.2   | Comparaison des performances sous trafic localisé                                   | 62         |

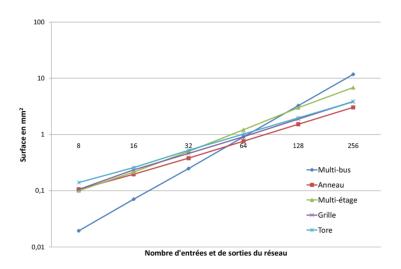

|          | 3.3            | Descri  | ption de la méthode de synthèse et résultats de synthèse ASIC                       | 67         |

|          |                | 3.3.1   | Méthodologie de synthèse                                                            | 67         |

|          |                | 3.3.2   | Résultat de synthèse                                                                | 67         |

|          | 3.4            | Comp    | araison des efficacités silicium des différentes topologies                         | 69         |

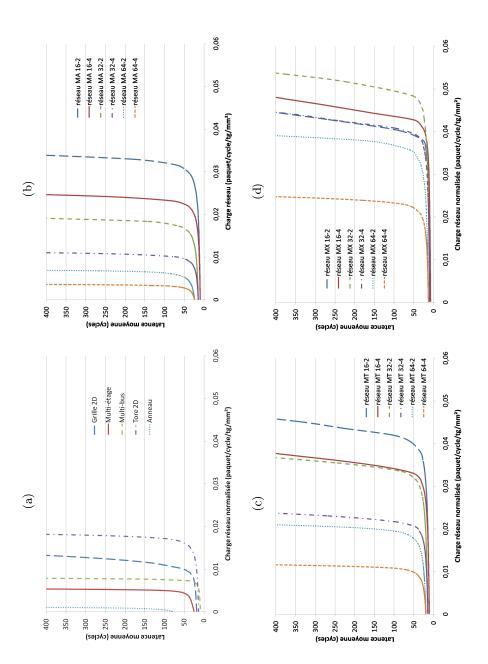

|          |                | 3.4.1   | Comparaison de l'efficacité surfacique sous trafic uniforme                         | 70         |

|          |                | 3.4.2   | Comparaison de l'efficacité surfacique sous trafic localisé                         | 73         |

|          | 3.5            | Concl   | usion sur le choix de la topologie                                                  | 74         |

| 4        | Mo             | dèle d  | exécution pour structures many-core hiérarchiques em-                               |            |

|          | bar            | quées   |                                                                                     | 77         |

|          | 4.1            | Préser  | ntation des familles d'algorithmes d'ordonnancement existants                       |            |

|          |                | dans l  | e domaine du calcul haute performance                                               | 78         |

|          |                | 4.1.1   | Les algorithmes par liste                                                           | 79         |

|          |                | 4.1.2   | Les algorithmes par groupe (Clusterisation)                                         | 81         |

|          |                | 4.1.3   | Exemple de réalisation pour une architecture many-core et conclusion sur l'existant | 83         |

|          | 4.2            | Descri  | aption des algorithmes de faible complexité sélectionnés et de                      | 00         |

|          | 1.2            |         | connement de test                                                                   | 84         |

|          |                | 4.2.1   | L'environnement de test                                                             | 85         |

|          |                | 4.2.2   | Les algorithmes d'ordonnancement par liste existants                                | 86         |

|          |                | 4.2.3   | Les nouveaux algorithmes d'ordonnancement par liste                                 | 86         |

|          |                | 4.2.4   | Les nouveaux algorithmes d'ordonnancement par groupe sta-                           |            |

|          |                | 1.2.1   | tique                                                                               | 88         |

|          |                | 4.2.5   | Le nouvel algorithme d'ordonnancement dynamique par groupe                          |            |

|          | 4.3            |         | en place de métriques et de moyens de mesure                                        | 90         |

|          | 4.4            |         | araison entre les différentes propositions d'algorithmes                            | 92         |

|          |                | 4.4.1   | Résultats avec un graphe hautement dépendant                                        | 93         |

|          |                | 4.4.2   | Résultats avec un graphe parallèle                                                  | 96         |

|          |                | 4.4.3   | Synthèse de l'étude sur les algorithmes d'ordonnancement de                         | 0 0        |

|          |                |         | faible complexité                                                                   | 99         |

|          | 4.5            | Propo   | sition d'un modèle d'exécution pour une architecture many-core                      |            |

|          |                | -       | chique                                                                              | 99         |

|          |                | 4.5.1   | <del>-</del>                                                                        | 100        |

|          |                | 4.5.2   |                                                                                     | 105        |

|          |                | 4.5.3   |                                                                                     | 106        |

### Table des matières

|    | 4.6    | Vérification des performances                                    |              |

|----|--------|------------------------------------------------------------------|--------------|

|    | 4.7    | Conclusion                                                       | 108          |

| 5  | Mis    | se en place d'une architecture et validation de l'architecture e | $\mathbf{t}$ |

|    | du :   | modèle d'exécution                                               | 109          |

|    | 5.1    | Description de notre architecture massivement parallèle          | 110          |

|    |        | 5.1.1 Vue d'ensemble du fonctionnement                           | 111          |

|    |        | 5.1.2 L'architecture globale                                     | 113          |

|    |        | 5.1.3 Le cluster matériel                                        | 116          |

|    | 5.2    | Une application de test                                          | 122          |

|    | 5.3    | Implémentation de notre architecture dans SESAM                  | 125          |

|    |        | 5.3.1 SESAM: Simulation Environment for Scalable Asymmetric      |              |

|    |        | Multiprocessors                                                  | 125          |

|    |        | 5.3.2 Implémentation de notre architecture dans SESAM            | 127          |

|    | 5.4    | Caractérisation de notre architecture hiérarchique               | 128          |

|    |        | 5.4.1 Dynamique versus Statique                                  | 129          |

|    |        | 5.4.2 Caractérisation de la hiérarchisation du contrôle          | 131          |

|    | 5.5    | Impact de la hiérarchisation sur la surface                      | 133          |

|    | 5.6    | Conclusion                                                       | 134          |

|    | Cor    | nclusions et Perspectives                                        | 135          |

|    |        | Synthèse des travaux                                             | 135          |

|    |        | Perspectives                                                     | 137          |

|    |        | A court terme                                                    | 137          |

|    |        | A long terme                                                     | 138          |

| Bi | ibliog | graphie                                                          | 141          |

| Pι | ublic  | ations personnelles                                              | 149          |

# Table des figures

| 1 2  | Besoin en calcul des applications embarquées                               | 3  |

|------|----------------------------------------------------------------------------|----|

| 1.1  | Liste non exhaustive des architectures MPSoC (MultiProcessor Sys-          |    |

|      | tem on Chip) en fonction du nombre de processeurs                          | 8  |

| 1.2  | Les interconnexions point à point                                          | 13 |

| 1.3  | Les interconnexions par bus                                                | 14 |

| 1.4  | Les réseaux sur puce                                                       | 16 |

| 1.5  | Routeur élémentaire                                                        | 18 |

| 1.6  | Représentation des topologies régulières.                                  | 23 |

| 1.7  | Représentation des topologies irrégulières.                                | 24 |

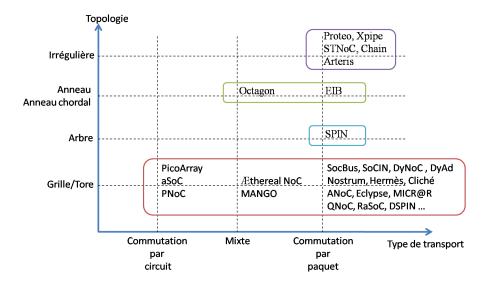

| 1.8  | Classification des réseaux                                                 | 31 |

| 2.1  | Vitesse de simulation des niveaux de modélisation en fonction de leurs     |    |

|      | précisions                                                                 | 34 |

| 2.2  | Timed TLM vs Approximated Time TLM                                         | 39 |

| 2.3  | Différence entre temps explicite et implicite dans le TLM                  | 41 |

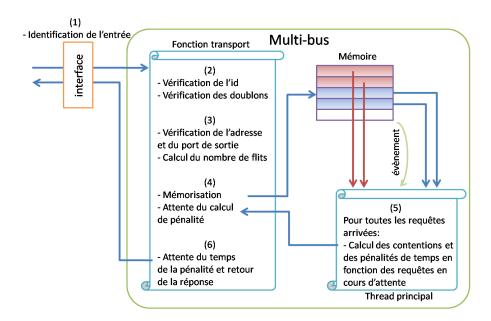

| 2.4  | Représentation du fonctionnement du simulateur de réseaux sur puce         | 43 |

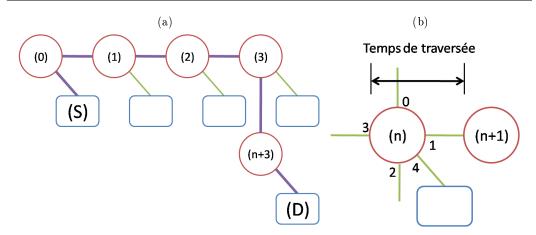

| 2.5  | Représentation d'un chemin dans le simulateur                              | 46 |

| 2.6  | Représentation de la structure de comparaisons des différentes topologies. |    |

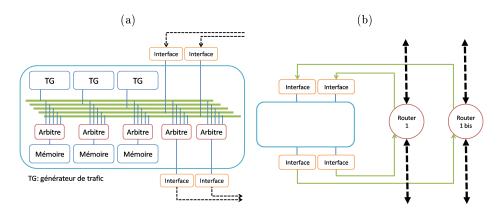

|      | (TG : générateur de trafic)                                                | 47 |

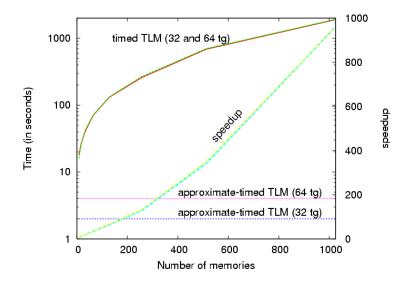

| 2.7  | Temps de simulation en fonction du nombre de mémoires dans les cas du      |    |

|      | TTLM et ATTLM. (TG : générateur de trafic)                                 | 49 |

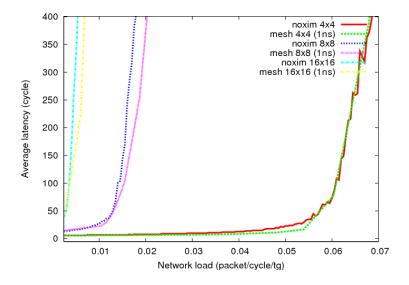

| 2.8  | Comparaison entre Noxim et notre approche                                  | 50 |

| 3.1  | Représentation d'un cluster matériel                                       | 57 |

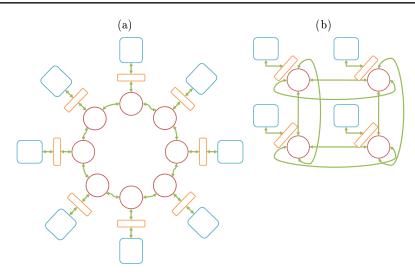

| 3.2  | Représentation de la topologie Multi-bus + Anneau et Multi-bus +           |    |

|      | Tore                                                                       | 58 |

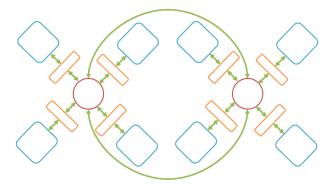

| 3.3  | Représentation de la topologie Multi-bus + Anneau amélioré                 | 58 |

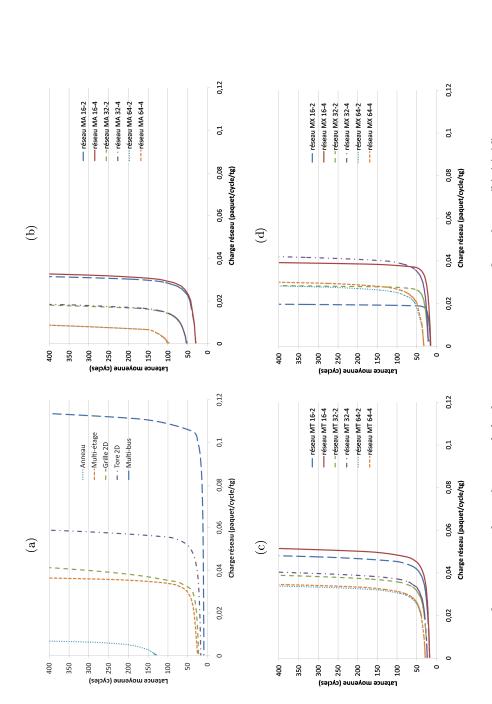

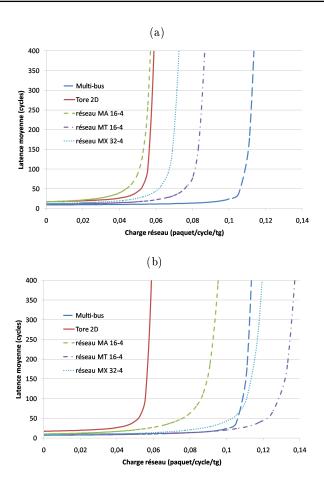

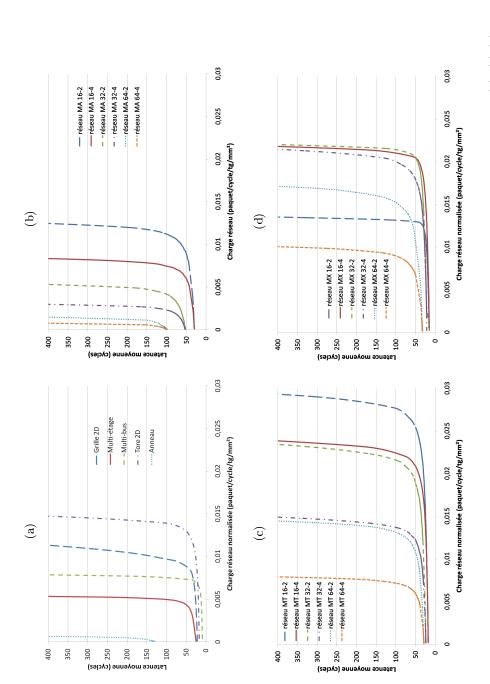

| 3.4  | Performance des réseaux pour un trafic uniforme                            | 60 |

| 3.5  | Performance des réseaux hiérarchiques pour un trafic pseudo-localisé.      | 63 |

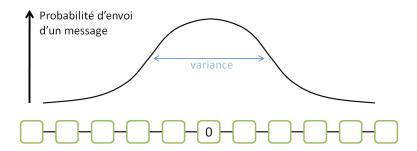

| 3.6  | Représentation de la probabilité d'envoi pour un trafic localisé sur un    |    |

|      | anneau.                                                                    | 64 |

| 3.7  | Performance des réseaux pour un trafic localisé                            | 66 |

| 3.8  | Courbe de surface des réseaux à plat                                       | 68 |

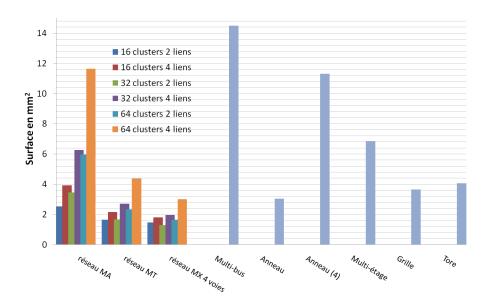

| 3.9  | Surface de tous les réseaux proposés pour 256 connexions                   | 70 |

| 3.10 | Efficacité surfacique des réseaux proposés pour un trafic uniforme         | 72 |

| 3.11 | Efficacité surfacique des réseaux proposés pour un trafic localisé         | 75 |

| 4.1  | Représentation du fonctionnement d'un algorithme par liste                 | 80 |

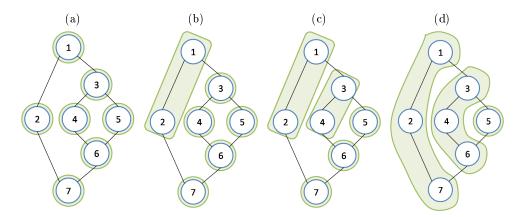

| 4.2  | Etapes de la clusterisation linéaire                                          | 82  |

|------|-------------------------------------------------------------------------------|-----|

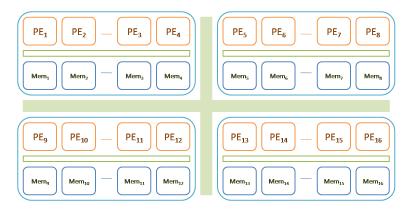

| 4.3  | Représentation de l'environnement synthétique de tests                        | 85  |

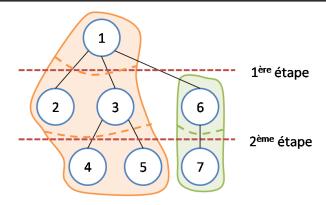

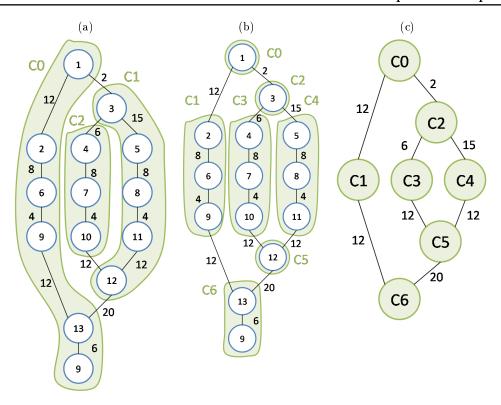

| 4.4  | Représentation de la découpe non-linéaire et dynamique en cluster de          |     |

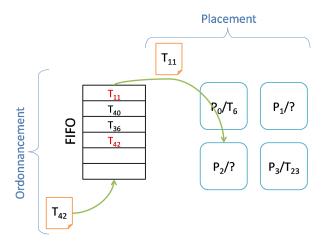

|      | l'algorithme Dynamic-Clustering-Mapping                                       | 90  |

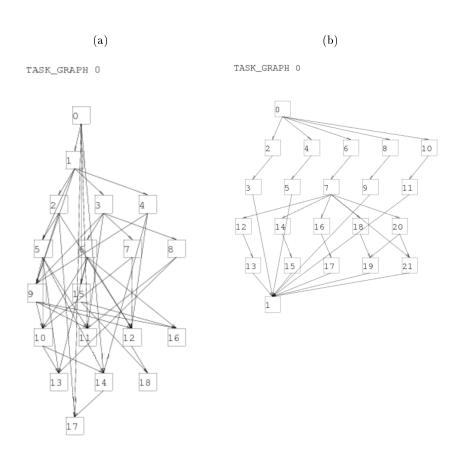

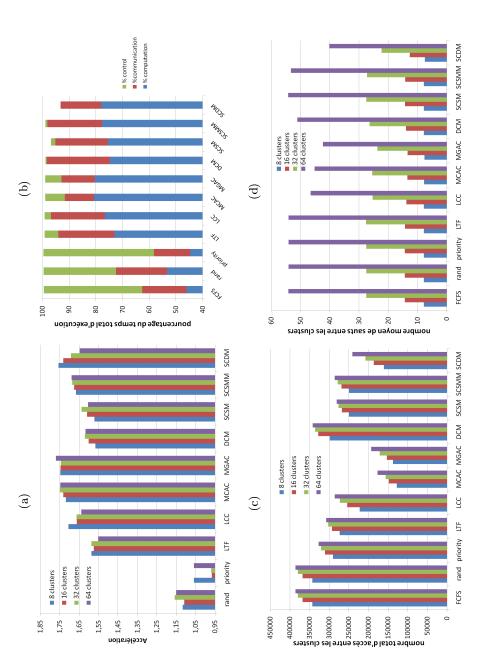

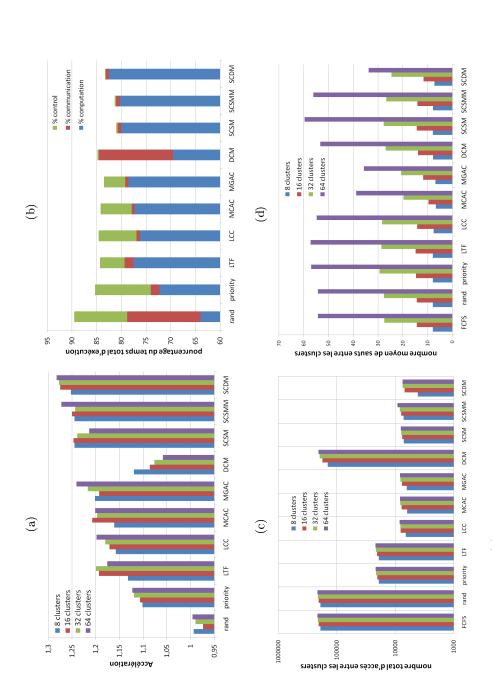

| 4.5  | Exemples de graphes générés avec TGFF                                         | 94  |

| 4.6  | Résultat des différents algorithmes pour un graphe hautement dépen-           |     |

|      | dant                                                                          | 95  |

| 4.7  | Résultat des différents algorithmes pour un graph parallèle                   | 98  |

| 4.8  | Modification de la clusterisation linéaire                                    | 102 |

| 4.9  | Représentation des informations nécessaire à l'ordonnancement                 | 103 |

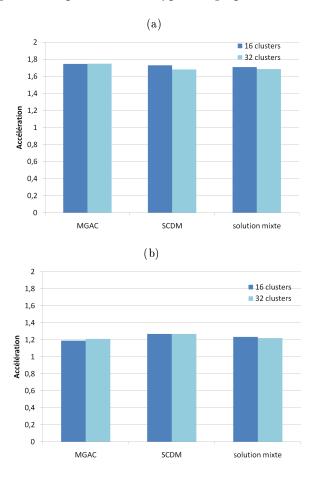

| 4.10 | Résultat de performances de notre solution                                    | 107 |

|      | 1                                                                             |     |

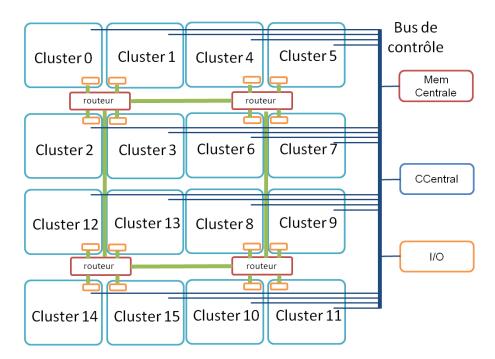

| 5.1  | Représentation de l'architecture globale                                      | 110 |

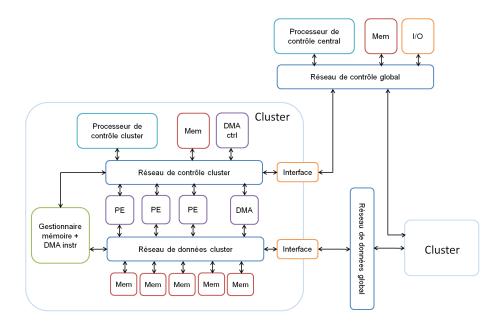

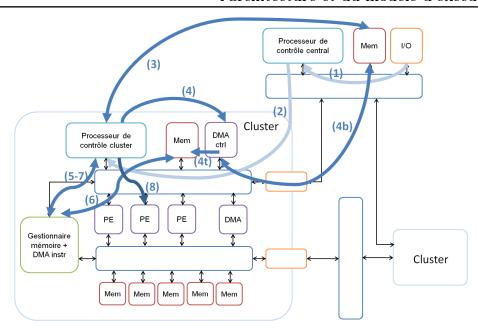

| 5.2  | Représentation du cluster de base                                             | 111 |

| 5.3  | Représentation des différentes étapes de lancement d'une application.         | 112 |

| 5.4  | Représentation du fonctionnement du TLB                                       | 114 |

| 5.5  | Représentation de la boucle d'ordonnancement du contrôle central              | 115 |

| 5.6  | Représentation de la boucle d'ordonnancement du contrôle cluster              | 118 |

| 5.7  | Pipeline de l'application de surveillance de carrefour. Pour chaque tâche, il |     |

|      | est mentionné si celle-ci est dynamique (ou non) et selon quels critères      | 123 |

| 5.8  | Représentation du graphe de tâches de l'application d'étiquetage              | 125 |

| 5.9  | Représentation d'une branche du graphe de tâches de l'application             |     |

|      | d'étiquetage.                                                                 | 126 |

| 5.10 | Images d'entrée et de sortie de l'application d'étiquetage                    | 126 |

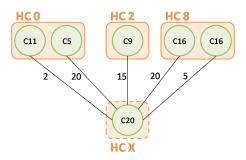

| 5.11 | Représentation de l'architecture contenant un contrôle hiérarchique.          | 127 |

| 5.12 | Image à labelliser contenant une fausse silhouette de piéton                  | 129 |

# Liste des tableaux

| 1.1 | Résumé des caractéristiques des différentes solutions                        | 17  |

|-----|------------------------------------------------------------------------------|-----|

| 3.1 | Estimation de la surface des interconnexions en $mm^2$                       | 68  |

| 3.2 | Estimation de surface des réseaux hiérarchiques                              | 69  |

| 5.1 | Temps d'exécution de l'application de test pour un placement statique ou     |     |

|     | dynamique.                                                                   | 130 |

| 5.2 | Temps d'exécution de l'application de test en fonction du type de placement. | 131 |

| 5.3 | Temps moyen d'ordonnancement durant l'application de test en fonction        |     |

|     | du type de contrôle.                                                         | 132 |

| 5.4 | Temps d'exécution de l'application de test en fonction du type de contrôle.  | 132 |

| 5.5 | Estimation de la surface des architectures en $mm^2$                         | 133 |

# Introduction

#### Sommaire

| Contexte de l'étude |  |  |  |  |  |  |  |  |  |  |  |  | 1 |

|---------------------|--|--|--|--|--|--|--|--|--|--|--|--|---|

| Plan du manuscrit . |  |  |  |  |  |  |  |  |  |  |  |  | 4 |

L'un des premiers systèmes embarqués fut l'Apollo Guidance Computer. Conçu par la société MIT Intrumentation Laboratory sous la direction de Charles Stark Draper, ce dispositif équipa les navettes et modules lunaires des missions Apollo dans les années 60-70 comme ordinateur de navigation et de pilotage. Il était composé d'environ 4500 portes NOR, 32 Kbits de mémoire vive et 576 Kbits de mémoire morte. L'ensemble du dispositif fonctionnait à 2 MHz et traitait des mots de 16 bits. Depuis cette révolution, les systèmes embarqués se sont répandus dans notre quotidien jusqu'à devenir quasiment indispensables. Poussés en permanence par la demande croissante des consommateurs, les systèmes embarqués n'ont cessé d'évoluer en termes de performance, de puissance de calcul et de capacité mémoire.

#### Contexte de l'étude

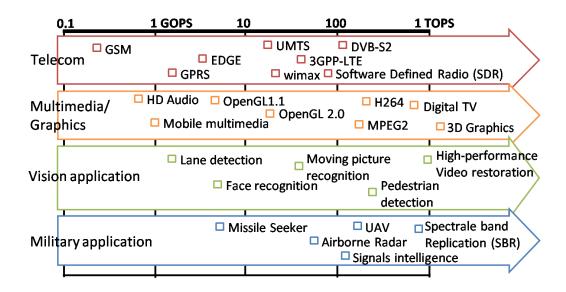

La conséquence majeure de cette demande des consommateurs est que les besoins en puissance de calcul sont devenus de plus en plus importants au fur et à mesure qu'évoluent les systèmes. La figure 1 fait apparaître les puissances de calcul nécessaires en fonction des applications pour différents domaines applicatifs. Ainsi, par exemple, dans le domaine des télécommunications, à mesure que les standards évoluent les besoins en puissance de calcul augmentent jusqu'à atteindre environ 50 Giga Opération Par Seconde (GOPS) pour le standard 3 GPP-LTE. On retrouve la même tendance dans le multimédia où, du fait de l'augmentation de la taille des images et de la complexité croissante des algorithmes de compression, de plus en plus de puissance de calcul est nécessaire. Par exemple, la décompression en H264 du flux d'une vidéo HD nécessite plus de 100 GOPS. Cette même évolution de la puissance de calcul touche tous les domaines de l'embarqué que ce soit pour les applications de vision ou encore les applications militaires.

De plus, aujourd'hui un téléphone, par exemple, ne doit pas seulement téléphoner mais également permettre de gérer ses mails, surfer sur internet, regarder des films en haute définition ou encore jouer à des jeux vidéo. Cette demande impose aux systèmes embarqués d'être capables d'exécuter un large panel d'applications provenant de domaines différents. Cette multiplication des domaines applicatifs pose un problème d'efficacité des dispositifs de calcul intégrés. En effet, dans le cas de calculs intensifs provenant de deux domaines différents, les calculs ne vont pas être réalisés sur les mêmes types de données. Ainsi, dans le domaine des télécommunications,

Fig. 1 — Le graphique représente les besoins en calcul de différentes applications regroupées par thème. (GOPS : Giga Opération Par Seconde; TOPS : Tera Opération Par Seconde)

les calculs sont souvent réalisés sur des données codées en virgule fixe sur 16 bits alors que dans le domaine graphique, les données manipulées sont plutôt codées en virgule flottante sur 32 bits. Il sera donc compliqué d'optimiser les processeurs pour supporter ces deux types de données.

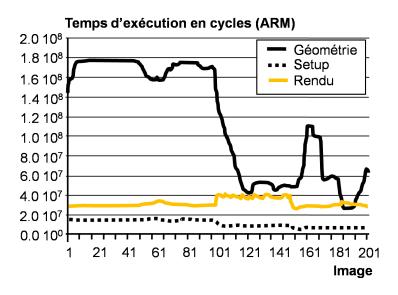

Enfin, en conséquence de cette évolution, les applications deviennent également de plus en plus dynamiques. En effet le temps d'exécution de ces applications dépend de paramètres non prédictibles au moment de l'écriture du programme. Ceci se traduit par un accroissement des séquences de contrôle dans le code du programme. On peut prendre comme exemple une application de reconnaissance de caractères. La séquence de reconnaissance de cette application va dépendre des caractères précédents ainsi que de la donnée courante. Et il n'est donc pas possible de prédire à l'avance le temps exact que va durer le traitement. En revanche, il est en général possible d'estimer une borne maximale au temps de traitement. Ceci se retrouve de plus en plus dans le domaine graphique, où les algorithmes s'adaptent aux données à traiter. Par exemple, dans [1], les auteurs présentent un pipeline de rendu 3D. Ils découpent le pipeline en trois phases (setup, géométrie et rendu) et pour chaque phase, ils mesurent le temps de calcul en fonction des images à créer. La figure 2 présente leurs résultats pour 201 images. Dans leur cas, la partie géométrie varie de plus d'un facteur 4 sur le temps d'exécution en fonction de l'image à créer. Ce dynamisme des applications implique qu'aucune solution optimale d'ordonnancement ne peut être réalisée hors-ligne et donc que le contrôle du système doit être lui-même dynamique afin de permettre une optimisation en ligne.

L'évolution des systèmes embarqués pose donc un problème au niveau de leur

Fig. 2 — Temps d'exécution en cycles d'un pipeline de rendu 3D en fonction de chaque image créée. Chacune des trois phases qui composent le pipeline sont détaillées. Les valeurs sont issues de [1].

conception car ces systèmes doivent trouver un compromis entre leurs capacités (puissance de calcul, dynamisme) et les contraintes des systèmes embarqués (surface silicium, consommation). Le problème de la puissance de calcul est celui qui a été résolu en premier même si augmenter la puissance de calcul tout en respectant les contraintes de surface et de consommation du domaine de l'embarqué n'est pas un problème aisé. En effet, afin d'augmenter la puissance de calcul d'un monoprocesseur, il est possible d'augmenter la taille des caches ainsi que la complexité des mécanismes de prédiction afin de limiter les cycles d'inactivité dans le processeur. Ces techniques augmentent, par la même occasion, la surface silicium et la consommation énergétique du processeur ce qui, en général, diminue l'efficacité surfacique et énergétique. Or ces deux paramètres sont des paramètres importants pour le domaine de l'embarqué. La solution envisagée pour adresser ce problème est de passer à des systèmes multiprocesseurs. D'après [2], il est plus efficace d'intégrer plusieurs petits processeurs, spécialisés ou non, dont les efficacités énergétique et silicium sont meilleures, que d'augmenter les performances d'un seul processeur. Ainsi, au total, on obtient une puissance de calcul crête équivalente à un monoprocesseur pour une consommation en surface et en consommation plus faible. Suivant cette tendance, l'ITRS [3] prévoit une croissance annuelle de plus de 32% du nombre de processeurs, pour les années à venir, jusqu'à atteindre plus de 800 processeurs en 2015.

En résumé, aujourd'hui les utilisateurs demandent d'avoir des systèmes embarqués performants capables d'offrir de grandes puissances de calcul pour un large spectre d'applications en respectant les contraintes du monde de l'embarqué. De plus, ces applications ont de plus en plus un comportement et un temps d'exécution non prédictible au moment de la compilation. Il est donc nécessaire de proposer

des architectures multiprocesseurs offrant une grande puissance de calcul pour plusieurs domaines d'application. Ces architectures doivent être gérées dynamiquement afin d'offrir les meilleurs performances. Le tout doit être fourni pour une empreinte silicium et énergétique les plus faibles possibles.

Les différentes architectures multiprocesseurs disponibles actuellement répondent en partie aux besoins exprimés mais jamais complètement. On retrouve deux catégories d'après l'étude menée par les auteurs de [4]. Soit ces architectures sont massivement parallèles mais ne gèrent que statiquement les applications, soit elles proposent une gestion dynamique des applications mais ne proposent pas une puissance de calcul suffisante.

### Plan du manuscrit

L'objectif de cette thèse est de mettre en place un modèle d'exécution adapté à la gestion de centaines de processeurs ainsi qu'une architecture multiprocesseur massivement parallèle programmable et homogène. Pour cela les aspects de communication puis de gestion dynamique d'application vont être explorés avant de proposer une solution au problème énoncé.

Le premier chapitre de ce document propose une étude des architectures multiprocesseurs représentatives des solutions contenant plus de 50 processeurs. Celle-ci montre que les infrastructures de communication ainsi que la gestion dynamique des applications sont deux problèmes importants dans les architectures massivement parallèles. C'est pourquoi, dans un premier temps, un état de l'art est réalisé sur les réseaux sur puce afin de choisir une interconnexion capable de connecter des centaines de processeurs et mémoires tout en gardant de bonnes performances. Les contextes de chaque étude étant différents, cet état de l'art met en évidence qu'il est très difficile de comparer tous les réseaux proposés. De plus, il en ressort également que la topologie ne peut pas être choisie facilement sans une phase d'exploration. Cette étude va tout de même permettre de choisir un certain nombre de topologies représentatives.

Le deuxième chapitre met en place une structure de simulation des réseaux sur puce qui va permettre de comparer les différentes topologies sélectionnées dans le premier chapitre. Avant de mettre en place ce simulateur, un niveau de simulation doit être défini afin de permettre le meilleur compromis entre précision et rapidité. Puis un état de l'art des simulateurs conclut qu'aucun simulateur ne propose de solutions permettant la comparaison de topologie au niveau de modélisation transactionnelle. Enfin le détail de notre simulateur de réseaux sur puce est donné dans ce chapitre.

Le troisième chapitre propose de présenter et commenter les résultats de la simulation des différentes topologies. Afin d'obtenir une comparaison en surface de ces réseaux, leurs synthèses ASIC ont été réalisées. Nous proposons une nouvelle façon d'analyser l'efficacité surfacique des réseaux en faisant apparaître la latence réseau en fonction de la charge réseau normalisée en surface. A l'issue de cette comparai-

#### Introduction

son, une topologie Multibus+Anneau amélioré sera sélectionnée pour son efficacité silicium.

Une fois la structure de communication mise en place, le quatrième chapitre propose une analyse de l'enjeu de la gestion des tâches qui est le deuxième problème des architectures massivement parallèles énoncé dans le chapitre 1. Pour cela un état de l'art des algorithmes en ligne provenant du calcul haute performance et utilisable dans l'embarqué est réalisé. Ensuite une comparaison des différents algorithmes est effectuées. Cette étude va faire apparaître les meilleurs algorithmes d'ordonnancement en fonction des types d'application. De ces résultats, nous proposons un modèle d'exécution hiérarchique et dynamique qui combine les résultats précédents afin d'offrir les meilleures performances quel que soit le type d'application.

Le cinquième chapitre propose une implémentation et une validation de l'architecture ainsi que des services du modèle d'exécution. L'architecture est implémentée dans un environnement de simulation. Afin de permettre une évalusation, notre architecture est comparée à une seconde utilisant un contrôle centralisé. Enfin différents tests vont être réalisés permettant d'évaluer le gain d'une gestion dynamique, de la hiérarchisation du contrôle ainsi que le surcoût de la migration.

Finalement, le dernier chapitre présente un résumé des contributions de ces travaux de recherche. Il propose une discussion sur la suite de ces travaux ainsi que des perspectives à plus long terme.

# Etat de l'art

| S                      | Λ | m   | m   | ai | r | Δ |

|------------------------|---|-----|-----|----|---|---|

| $\mathbf{\mathcal{L}}$ | v | TIT | 111 | aı |   | _ |

| 1.1 Les architectures multiprocesseurs existantes .                      | <br>8         |

|--------------------------------------------------------------------------|---------------|

| 1.1.1 Les solutions statiques                                            | <br>9         |

| 1.1.2 Les solutions dynamiques                                           | <br>10        |

| 1.1.3 Conclusion sur les architectures multiprocesseurs                  | <br>11        |

| 1.2 Choix d'un type d'interconnexion                                     | <br><b>12</b> |

| 1.2.1 Connexion point à point                                            | <br>12        |

| 1.2.2 Connexion par bus                                                  | <br>13        |

| 1.2.3 Réseaux sur puce : NoC (Network on Chip)                           | <br>14        |

| 1.2.4 Synthèse sur les modes de communication                            | <br>16        |

| 1.3 Les caractéristiques des réseaux sur puce                            | <br>17        |

| 1.3.1 L'étude théorique des réseaux sur puce                             | <br>17        |

| $1.3.2  \text{Les \'el\'ements de base des NoC} \ . \ . \ . \ . \ . \ .$ | <br>18        |

| 1.3.3 Les mécanismes de transport                                        | <br>19        |

| 1.3.4 La topologie                                                       | <br>21        |

| 1.3.5 Les algorithmes de routage                                         | <br>26        |

| 1.3.6 Le contrôle de flux $\dots$                                        | <br>27        |

| 1.3.7 Qualité de service (Quality of Service : QoS)                      | <br>29        |

| 1.4 Conclusions de l'état de l'art                                       | <br><b>30</b> |

La course pour l'augmentation de la puissance de calcul des processeurs embarqués est régie par les contraintes de surface et de consommation électrique. Or l'augmentation de la puissance de calcul d'un monoprocesseur impose une augmentation de sa complexité et donc réduit son efficacité énergétique et surfacique. C'est pourquoi, l'on s'oriente maintenant vers les structures multiprocesseurs en grande partie car il est moins coûteux de mettre sur une puce plusieurs processeurs, plus petits et plus efficaces d'un point de vue silicium et consommation, qu'un seul processeur pour des performances théoriques équivalentes.

Afin de mieux comprendre l'état de l'art multiprocesseur, ce chapitre détaille cinq architectures qui répondent le plus aux besoins de puissances de calcul et de dynamisme. Cependant aucune ne répond complètement au problème. Pour les architectures offrant le plus de dynamisme, il apparaît que c'est l'interconnexion et le modèle d'exécution qui freinent l'augmentation du nombre de processeurs. Nous allons d'abord nous pencher sur le problème de l'interconnexion. C'est pourquoi dans un deuxième temps, ce chapitre présente un état de l'art des interconnexions sur puce et détaille les différentes caractéristiques des réseaux sur puce.

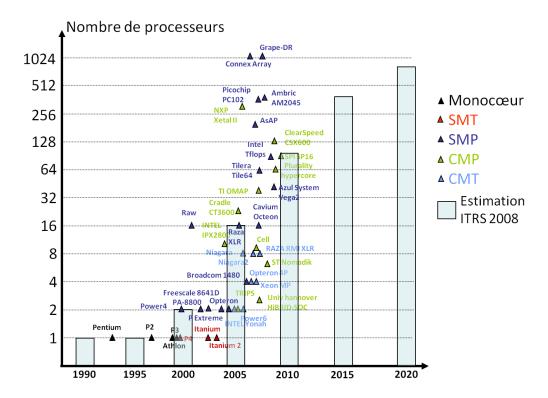

### 1.1 Les architectures multiprocesseurs existantes

La figure 1.1 superpose l'estimation ITRS (International Technology Roadmap for Semiconductors) concernant l'évolution des architectures multiprocesseurs avec la réalité des puces réalisées et détaillées dans [4]. Il apparaît que la tendance suivie par les industriels et les académiques suit la vision de l'ITRS ce qui tend à confirmer les estimations. Parmi tous les multiprocesseurs, la volonté principale des concepteurs est de fournir une puissance de calcul maximale. Pour cela, ils adoptent différents modèles d'exécution (axé flot de données, axé contrôle), et différentes structures matérielles (mer de processeurs, approche symétrique ou asymétrique).

FIG. 1.1 — Le graphique représente une liste non exhaustive d'architectures mono et multi processeurs en fonction de leur nombre de processeurs et de leur année de fabrication. L'estimation de l'ITRS se superpose à la réalité. Les processeurs sont référencés en fonction de leur structure. SMT signifie Simultaneous MultiThreading, SMP : Symetric MultiProcessor, CMP : Chip MultiProcessors et CMT : Chip MultiThreading.

Comme nous l'avons dit plutôt, l'augmentation de la puissance de calcul passe par l'accroissement du nombre de cœurs. Ces cœurs peuvent être soit homogènes, soit hétérogènes. Les solutions hétérogènes cherchent à répondre aux besoins de puissance de calcul en plaçant sur la puce des modules dédiés à chaque domaine d'application. Les solutions homogènes cherchent à être flexibles en proposant seulement un type de cœur. Les solutions proposant les plus grands nombres de cœurs sont

toutes des solutions homogènes. Parmi ces architectures, on trouve deux stratégies de contrôle. Soit l'architecture propose une solution avec un placement statique des applications sur l'architecture, soit les applications sont déployées dynamiquement sur l'architecture. Selon les solutions, le problème de dynamisme des applications est pris ou non en considération. Cinq architectures représentatives des solutions existantes ont été choisies pour être détaillées.

#### 1.1.1 Les solutions statiques

Les solutions de PICOCHIP [5], ASAP [6] et AMBRIC [7] sont basées un modèle de programmation statique. Les solutions de PICOCHIP et d'AMBRIC se focalisent sur des domaines d'application précis qui sont respectivement les télécommunications et le traitement d'images.

PICOCHIP propose ainsi un multiprocesseur composé de plus de 300 processeurs élémentaires. Les processeurs sont répartis par groupes de quatre. Ces groupements sont connectés à deux bus. Ces deux bus relient deux routeurs entre eux. Ceux-ci forment un réseau sur puce en grille à travers toute la puce. Afin d'optimiser le fonctionnement, toutes les applications sont placées statiquement sur la puce. Cette opération est aidée par la suite logicielle mise à la disposition de l'utilisateur. L'ensemble des communications à travers le système est donc déterminé au moment de la compilation de l'application. Ceci permet donc de s'affranchir d'arbitrage entre les communications pendant l'exécution. Cette technique de communication simplifie grandement le réseau d'interconnexion. Cependant il est nécessaire de déterminer, hors-ligne à l'aide des outils, le fonctionnement de l'application et donc de prendre en compte les pires cas d'exécution afin d'assurer un bon fonctionnement du système. Cette solution offre de très bonnes performances, mais le placement statique ne permet pas d'optimiser au mieux l'utilisation des ressources de calcul pour les applications dynamiques.

AMBRIC propose, dans son cas, un multiprocesseur dédié aux applications de traitement d'images. Ce multiprocesseur contient plus de 300 DSP (Digital Signal Processor). Les processeurs et les mémoires sont placés sur la puce selon un damier. Les cases sont connectées avec leurs proches voisines. Chacune de ces connexions est réalisée par un lien dédié. Le non partage des liens permet d'assurer qu'aucune contention ne viendra diminuer les performances. Du fait de la structure de l'architecture, les applications sont découpées en objets. L'ensemble de l'application cascade un certain nombre de ces objets. Chaque objet est placé soit sur un processeur, soit sur plusieurs processeurs voisins. L'ensemble du placement est défini statiquement. Comme pour le multiprocesseur de PICOCHIP, des outils sont fournis afin d'aider le placement et la programmation de la puce. Mais dans le cas d'AM-BRIC, la problématique de la gestion des communications est grandement simplifiée car il n'y a pas de partage des liens de communication. Le modèle de programmation ne permet que de réaliser du flot de données. Cette solution obtient, comme dans le cas du PICOCHIP, de bonnes performances, en contrepartie les applications sont placées statiquement ce qui ne permet pas d'optimiser l'utilisation des ressources de

calcul dans le cas d'applications dynamiques.

L'architecture « Asynchronous Array of Simple Processors » (AsAP) propose pour sa part d'élargir le spectre des applications visées. Cette architecture comporte 164 processeurs génériques plus 4 modules de calcul dédiés à certain domaine (Viterbi, FFT...). Chaque processeur est associé à une mémoire d'instructions et de données ainsi qu'à un routeur afin de former une tuile. Chaque tuile possède sa propre horloge afin d'adapter sa fréquence aux besoins de calcul. Toutes les tuiles sont connectées à travers un réseau sur puce disposé en grille. Chaque routeur est contrôlé par le processeur de la tuile. C'est le processeur qui configure les connexions dans le routeur. Afin de simplifier les communications, le signal d'horloge de la source est envoyé en même temps que la donnée. Du fait des horloges séparées, des FIFO à double horloge sont installés entre les tuiles et le routeur. Les applications exécutées sur la puce doivent être décrites dans un modèle flot de données. Ensuite chaque tâche de l'application est placée statiquement sur une tuile afin de limiter les distances de communication. Cette architecture permet de reconfigurer chaque routeur de la puce et ainsi de faciliter les communications dynamiques entre les tuiles. Cependant les différentes tâches sont placées statiquement sur l'architecture. Cette architecture propose un compromis entre une solution complètement statique et une solution complètement dynamique.

Les solutions de ce type intègrent des centaines de processeurs homogènes. La programmation de ces structures passe par une phase d'optimisation statique afin d'obtenir les performances attendues. Du fait qu'aucune optimisation en ligne n'est réalisée, le dimensionnement doit se faire au pire cas afin de garantir l'exécution et les performances. Ceci limite donc la charge effective de ces architectures.

#### 1.1.2 Les solutions dynamiques

La deuxième philosophie est de prendre le problème en entier et de proposer des multiprocesseurs multi-domaine afin d'exécuter n'importe quelle application dynamiquement. Les solutions proposées par PLURALITY [8] ou TILERA [9] sont de ce type.

La société TILERA propose un multiprocesseur multi-domaine. Celui-ci est composé de 64 processeurs élémentaires avec leur cache. Chaque processeur est connecté avec son cache sur un routeur d'un réseau-sur-puce. Chaque ensemble processeur+mémoire cache est nommé tuile. La particularité est que chaque tuile peut exécuter un noyau linux seul. De plus, il est possible de définir statiquement des zones constituées de plusieurs tuiles où un noyau Linux SMP peut s'exécuter. Les tuiles sont organisées selon une grille. Afin de permettre la cohérence de données à travers toute la puce, un système de cohérence distribué sur tous les caches est mis en place. La gestion mémoire permet l'utilisation de la mémoire aussi bien dans un mode à mémoire partagée que dans un mode de passage de messages. Le plus de cette architecture est de simplifier le portage des applications sur cette architecture grâce à l'utilisation d'un noyau Linux. Toutefois, cette structure en grille limite la possibilité d'ajouter de nouveaux éléments sans diminuer les performances. En-

fin cette architecture offre une gestion dynamique des applications mais seulement sur un nombre statique de processeurs ce qui ne permet pas d'optimiser le taux d'utilisation de la puce.

La société PLURALITY propose une architecture à mémoire partagée. Elle peut être constituée de 16 à 256 processeurs élémentaires tous connectés à un contrôleur central. Une interconnexion Crossbar découpée en étages permet de relier tous les processeurs à tous les bancs mémoires avec un accès uniforme. Ceci permet d'éviter les problèmes d'engorgement comme dans le cas de TILERA. Cette architecture adopte un modèle de programmation par tâche. Chacune de ces tâches sera dupliquée et exécutée en parallèle en fonction du taux de parallélisme souhaité. Le contrôleur centralisé permet de placer dynamiquement les tâches sur les différents processeurs. Une particularité de l'architecture est de permettre un accès uniforme à la mémoire sans se soucier du placement des tâches et ainsi de réaliser simplement un équilibrage de charges à travers toute l'architecture. Cette structure permet donc d'appréhender le côté dynamique des applications ainsi que la nécessité d'exécuter des applications provenant de plusieurs domaines. Cependant la structure de l'architecture contraint la taille de la structure et limite ses performances. En effet afin de maintenir un accès uniforme entre les processeurs et les mémoires, l'interconnexion risque d'augmenter la surface de manière non linéaire par rapport au nombre de processeurs. Ceci aura pour impact de diminuer l'efficacité surfacique. Le problème majeur de cette architecture réside dans son modèle de programmation qui limite les possibilités de programmation. Ainsi ce modèle ne permet de créer que du parallélisme régulier. De plus, le streaming n'est pas supporté par l'architecture.

Ces deux architectures visent un large spectre de domaines applicatifs avec un contrôle dynamique. Toutes les deux proposent une solution homogène dynamique qui offre un début de flexibilité. Cependant les deux proposent des structures de communication qui limitent l'augmentation du nombre de processeurs. De plus les deux architectures utilisent des modèles d'exécution qui ne permettent pas soit d'utiliser dynamiquement l'ensemble des processeurs (TILERA), soit qui limitent l'expression du parallélisme (PLURALITY).

#### 1.1.3 Conclusion sur les architectures multiprocesseurs

Toutes les architectures présentées sont constituées de processeurs homogènes. Ce choix permet de faciliter la programmation de l'architecture ainsi que de simplifier le contrôle par rapport à des systèmes hétérogènes. De plus, l'homogénéité des processeurs permet une conception plus simple de la puce. C'est pour les mêmes raisons que nous avons également choisi de nous placer dans le cas de processeurs homogènes.

Les architectures multiprocesseurs embarquées sont capables soit d'une grande puissance de calcul en offrant plus de 300 processeurs sur une même puce comme le propose PICOCHIP; soit d'une gestion dynamique d'application sur un petit nombre de processeurs comme le propose TILERA. Cependant aucune architecture ne permet la gestion dynamique d'un grand nombre de processeurs. Actuellement

les architectures sont limitées par leur infrastructure de communication mais surtout leur modèle d'exécution borne le dynamisme afin de simplifier la gestion des processeurs.

Nous venons donc de voir qu'augmenter le nombre de processeurs sur une puce ajoute de nouveaux problèmes à la conception de celle-ci. Nous allons traiter, dans un premier temps, le problème de l'infrastructure de communications. Celle-ci doit donc d'après nos conclusions permettre l'augmentation du nombre de processeurs sur la puce.

De plus comme nous l'avons mentionné dans l'introduction, les applications embarquées qui demandent toute cette puissance de calcul deviennent de plus en plus dynamiques ce qui limite l'efficacité des ordonnancements statiques. L'utilisation d'ordonnancement dynamique, afin d'optimiser l'exécution des applications dynamiques, rend pour sa part difficile la prédiction des communications entre les éléments du multiprocesseur.

C'est pourquoi les sections suivantes vont explorer le domaine de conception des interconnexions sur puce afin de déterminer quelle est l'interconnexion la plus efficace dans un contexte non prédictible où un grand nombre de modules doit être connecté.

### 1.2 Choix d'un type d'interconnexion

Les réseaux sur puce sont devenus une des solutions incontournables. Cette première partie va permettre de comprendre pourquoi il existe un tel engouement autour de ces réseaux sur puce.

Pour répondre au besoin en puissance de calcul dans les systèmes embarqués, de plus en plus d'éléments de calcul sont placés sur une même puce. Face à ces besoins en communication, trois grandes familles d'interconnexion sur puce existent et vont être détaillées.

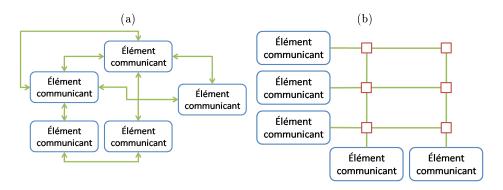

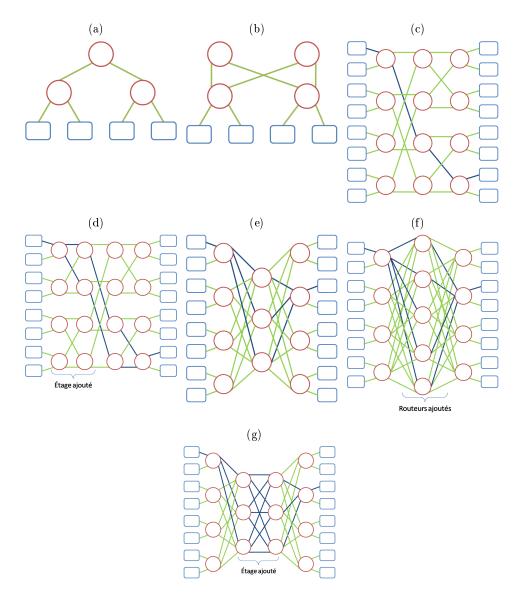

#### 1.2.1 Connexion point à point

La connexion point à point consiste à créer un lien de communication spécialisé entre chaque élément à interconnecter (Figure 1.2(a)). Ainsi lorsqu'une communication doit être réalisée, l'émetteur place le message sur le lien dédié et le récepteur renvoie une confirmation de réception. Ce type de connexion a l'avantage d'être extrêmement performant puisque qu'aucun partage de support de communication n'est réalisé. Il n'y a donc aucun arbitre ou autre stratégie de partage de ressources à mettre en place. Cependant du fait qu'un lien est créé entre chaque module qui communique, il est nécessaire de connaître à l'avance qui communiquera avec qui ou de connecter l'ensemble des modules entre eux dans un cas non prédictible. Dans notre contexte de contrôle dynamique, tous les modules sont a priori susceptibles de communiquer entre eux et donc toutes les possibilités d'interconnexion doivent être envisagées. Ceci conduit à un nombre important de liens et donc à une consommation importante de surface.

#### 1.2. Choix d'un type d'interconnexion

Cependant afin de réduire la surface de ce genre de connexion, il est possible de limiter le nombre d'entrée/sortie. Ainsi le Crossbar (Figure 1.2(b)) propose une solution pleinement connectée dont chaque élément possède une seule entrée/sortie. Dans ce cas, un arbitrage devient nécessaire pour n'avoir qu'un seul message à la fois à chaque entrée. IBM propose le Cyclops64 Crossbar étudié dans [10] qui permet de connecter jusqu'à 95 éléments. La complexité d'un Crossbar augmente avec le carré du nombre d'éléments connectés. Il est donc évident que ce genre d'interconnexion limite le nombre d'éléments interconnectés si la surface est une contrainte forte. Les connexions point à point possèdent les meilleures performances quelque soit le nombre d'éléments mais en contrepartie leur coût en surface est élevé.

Fig. 1.2 – (a) Représentation d'une connexion point à point, (b) Représentation d'un Crossbar

#### 1.2.2 Connexion par bus

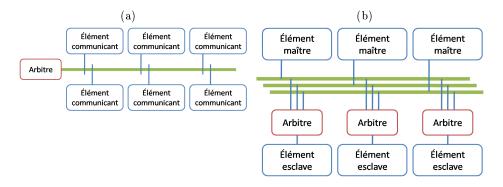

A la différence des interconnexions point à point, le bus cherche à partager les ressources de communication. Il est donc constitué de deux éléments principaux : un arbitre et un support de communication. Ce support de communication relie tous les éléments communicants (Figure 1.3(a)). Ainsi lorsqu'un élément veut envoyer un message sur le support de communication, il consulte tout d'abord l'arbitre afin d'ajouter sa requête sur une liste d'attente. Une fois qu'il a reçu l'autorisation, il envoie le message sur le support. Tous les éléments connectés reçoivent le message et seuls les destinataires du message le mémorisent. L'identification du ou des destinataires est réalisée à l'aide d'une adresse envoyée avant ou en même temps que le message. A tout moment il n'y a qu'un seul message sur le support de communication. Ce mode de fonctionnement partage les ressources de communication entre tous les éléments. Il existe une multitude de styles d'arbitrage qui dépendent des contraintes données. Ainsi, on trouve des arbitrages très simples comme le First In First Out (FIFO) qui est un arbitrage centralisé ou le Time Division Multiple Access (TDMA) qui est distribué à chaque interface. D'autres arbitrages plus compliqués existent également prenant en compte des priorités sur les émetteurs des messages par exemple.

Le bus est l'interconnexion la plus répandue du fait de sa simplicité de fonctionnement. De plus, le fait de partager un seul lien entre tous les modules lui permet d'être pleinement connecté avec un minimum de coût en surface. Cependant l'unicité du support de communication et donc le partage de la bande passante impose une limite au nombre d'éléments connectés. Dans le cas où tous les éléments connectés se partagent le temps d'accès au bus, au-delà d'une dizaine d'éléments maîtres (qui émettent des requêtes) sur le bus, on peut estimer que l'attente avant l'envoi du message devient non négligeable. Afin d'augmenter le nombre d'éléments sans trop sacrifier les performances, il est possible de connecter entre eux plusieurs bus à l'aide de ponts afin de cloisonner les communications. Ainsi le nombre d'émetteurs sur chaque bus diminue, ce qui augmente la part de bande passante pour chaque émetteur. On retrouve différents industriels proposant chacun leur bus. Ainsi ARM propose le Bus AMBA [11], ST Microelectronics le STBus [12] ou encore IBM le CoreConnect [13].

D'un autre côté, les communications entre éléments de deux bus différents sont complexifiées par le passage des différents ponts. Afin d'augmenter les performances, il est également possible de multiplier le nombre de bus disponibles afin de limiter les effets d'engorgement dus au partage des liens. On nommera ce genre d'interconnexions multi-bus (Figure 1.3(b)). Ceux-ci peuvent être vus comme un Crossbar incomplet. Augmenter le nombre de bus a pour effet de multiplier la bande passante et donc les performances mais étend par la même occasion la surface. En résumé, le bus est une solution simple et peu coûteuse d'un point vue surface. Les performances d'un bus sont contraintes par le nombre d'écrivains potentiels sur le bus ce qui pose problème pour de gros systèmes. Cette interconnexion a pour avantage de proposer une solution qui supporte naturellement les communications non prédictibles.

Fig. 1.3 – (a) Représentation d'un bus, (b) Représentation d'un multi-bus

#### 1.2.3 Réseaux sur puce : NoC (Network on Chip)

Du fait des limitations des bus et des connexions point à point, en ce qui concerne respectivement les performances et la surface, il est devenu nécessaire de proposer une nouvelle solution modulaire. Ainsi dès le début des années 2000 [14], W.J.

Dally et B. Towles formalisent la notion de NoC afin de remplacer les connexions longues distances sur les puces. Les réseaux sur puce dérivent des réseaux entre ordinateurs. Ils possèdent des caractéristiques similaires même si les contraintes sont différentes. Ainsi l'idée de base est de faire circuler l'information dans le réseau sur puce sous forme de messages découpés en paquets. Comme les réseaux Ethernet, ils sont constitués d'un ensemble de liens et de routeurs permettant la communication entre les éléments communicants (Figure 1.4(a)). Une interface réseau est placée entre le routeur et l'élément afin de mettre en forme le message. Les réseaux sur puce permettent de créer toutes les combinaisons possibles de routeurs et de liens. Ils sont donc modulaires selon les contraintes imposées. Cette modularité permet l'ajout de nouveaux éléments communicants sans avoir un impact important sur les performances comme pour le bus. De plus, cet ajout d'éléments se fait avec un minimum de liens ce qui limite son coût à la différence des connexions point à point.

Une autre notion adaptée aux NoC est la notion de couches [15, 16]. On retrouve les sept couches réseaux du modèle OSI (physique, liaison, réseau, transport, session, présentation et application) telles qu'on les voit sur la Figure 1.4(b). On retrouve d'ailleurs sur cette figure la partie du NoC réalisant les différentes couches. Dans l'ordre de la couche physique à la couche application,

- La couche physique définit les moyens physiques mis en œuvre pour le transport de l'information ainsi que les caractéristiques à respecter. Par exemple, pour le transport électrique, les informations de tension, de temps, etc. sont définies.

- La couche liaison assure le transfert d'un noeud à l'autre ainsi que de la fiabilité des transferts. Cette couche s'occupe donc du partage des liens physiques en intégrant de l'arbitrage. Cet arbitrage peut se faire, par exemple, par du TDMA ou encore par jeton (« Token Ring »). Elle peut mettre en place aussi des fonctions de détection et de correction d'erreurs afin d'assurer la fiabilité.

- La couche réseau met en place les techniques de routage à l'intérieur du réseau. Ces routages peuvent être statiques et offrir un seul chemin possible, dynamique et offrir des chemins multiples en fonction de l'engorgement du réseau. Cette couche permet d'abstraire la topologie et les liens du réseau.

- La couche transport s'occupe des fonctions au niveau paquet. Ainsi ce niveau découpe ou assemble les messages. Cette couche s'occupe également du contrôle des paquets à l'envoi et à la réception (« end-to-end »). Elle abstrait toutes notions de paquets pour les couches supérieures.

- La couche session gère les notions de synchronisation entre les modules. Elle permet de vérifier la bonne réception des messages. Elle offre aussi la possibilité d'établir une connexion entre deux modules, de la maintenir et de la fermer.

- La couche présentation prend en charge la transformation des formats des différents messages afin de permettre la bonne communication. Un exemple simple est la transformation d'une requête provenant d'un processeur en un message géré par le réseau.

- La couche application permet d'ajouter une dernière couche d'abstraction afin de simplifier l'envoi de données tel qu'une trame vidéo. De cette façon, aucune

contrainte due au réseau sur puce n'est visible depuis le niveau utilisateur, ce qui facilite son utilisation.

De plus, l'utilisation des réseaux par rapport au bus ou au point à point permet d'ajouter de nouveaux services dans les interconnexions sur puce. On peut citer par exemple la détection et la correction d'erreurs au niveau du message. Ils offrent une solution pleinement connectée grâce aux mécanismes de routage avec de bonnes performances et qui autorisent le partage de ressources. Ceci répond à nos besoins de connectivité, de performance tout en prenant en compte les contraintes de l'embarqué. En contrepartie, l'ajout d'interfaces réseaux augmente la latence d'envoi et de réception d'un message et pénalise le réseau par un surcoût en surface qui n'existe pas dans le cas du bus et des connexions point à point. Nous allons détailler par la suite les paramètres des réseaux sur puce sans approfondir la couche physique des réseaux. Pour plus d'information sur cette dernière, [17] détaille les couches physique et liaison.

Fig. 1.4 – (a) Réseau sur puce constitué de liens et de routeurs, (b) Les différentes couches réseau et leur implémentation

#### 1.2.4 Synthèse sur les modes de communication

Dans cette section, nous avons détaillé les différents types d'interconnexions répandues dans le monde des systèmes embarqués. Le tableau ci-dessous récapitule les caractéristiques de chacun. Un point important par rapport à notre contexte est la « scalabilité » de l'interconnexion choisie. On dit d'un système qu'il est « scalable » lorsque ce système est capable de garder ses caractéristiques lors de l'augmentation de sa taille.

Nous avons expliqué l'arrivée des réseaux sur puce dans le domaine de l'embarqué par une nécessité de connecter de plus en plus d'éléments sans sacrifier les performances et en limitant le surcoût en surface. Les réseaux sur puce permettent le partage de liens comme dans le bus tout en gardant de bonnes performances vis-à-vis des connexions point à point. Ils introduisent de nouvelles possibilités telles que la correction d'erreurs ce qui ajoute de la fiabilité. Ils nous permettent donc de

#### 1.3. Les caractéristiques des réseaux sur puce

| Type d'interconnexions       | Bus  |     | Point à point |     | Réseau sur Puce |     |

|------------------------------|------|-----|---------------|-----|-----------------|-----|

| Nb d'éléments interconnectés | <=10 | >10 | <=10          | >10 | <=10            | >10 |

| Performance                  | +    |     | ++            | ++  | +               | +   |

| Surface                      | ++   | ++  | -             |     | -               | -   |

| « Scalabilité" +             |      |     | -             |     | -               | ++  |

TAB. 1.1- Résumé des caractéristiques des différentes solutions. Les signes +/- permettent de caractériser les différents points caractéristiques recherchés. Le signe + indique que l'interconnexion obtient de bons résultats et inversement pour le signe -. Le nombre de signe pondère la caractérisation.

connecter des dizaines de modules dans des conditions optimales et en permettant le côté non prédictible des communications.

Les réseaux sur puce semblent répondre à nos attentes cependant l'espace de conception est très vaste. C'est pourquoi la section suivante décrit et commente les caractéristiques principales des réseaux sur puce à l'aide d'une étude bibliographique.

### 1.3 Les caractéristiques des réseaux sur puce

Cette section présente tout d'abord le point de vue théorique de l'étude des réseaux. Puis elle propose une description pratique des différentes caractéristiques des réseaux sur puce et analyse chacune d'entre elles. Cette étude a pour but de déterminer quelles sont les caractéristiques possibles dans le cas d'une architecture massivement parallèle sur puce. Pour cela, dans un premier temps, il est nécessaire de connaître les différents éléments d'un réseau sur puce. Et dans un deuxième temps, cette section présente les différentes possibilités pour chaque caractéristique.

#### 1.3.1 L'étude théorique des réseaux sur puce

Les réseaux, en général, peuvent être vus d'un point vue théorique. On retrouve de nombres ouvrages, [18, 19] par exemple, qui traitent de cette problématique. Dans ce cas, le réseau est vu comme un graphe où chaque routeur est considéré comme un noeud du graphe et chaque lien comme un arc du graphe. Un réseau se résume, ensuite, à une suite de propriétés mathématiques et de paramètres tels que le diamètre du réseau qui correspond à la distance moyenne parcourue dans le réseau, ou encore le degré des routeurs qui correspond au nombre d'entrées et de sorties de celui-ci.

Plus récemment, le network calculus [20] est un environnement permettant l'analyse des performances et des garanties de bande passante dans le réseau. Cet environnement reprend les théories sur les réseaux. Il se base sur l'enveloppe du trafic dans le réseau, les contraintes des liens ou encore sur la gestion de la congestion afin de calculer la taille des mémoires tampon dans le système ou encore les délais d'un point à un autre.

Ces études théoriques sont adéquates dans le cas de grands réseaux où le nombre

de routeurs dépasse le millier et que le réseau devient difficilement analysable par simulation ou dans un cas de contraintes dures de fiabilité. Dans notre cas, le réseau comporte quelques centaines de routeurs ce qui reste raisonnable pour une étude pratique. C'est pourquoi la suite de ce chapitre traite les réseaux d'un point de vue pratique et non théorique.

#### 1.3.2 Les éléments de base des NoC

Ce paragraphe détaille les différents constituants des réseaux sur puce afin d'introduire le vocabulaire utilisé dans le reste de la section. Dans un réseau, les différents modules envoient des paquets de données. Ces paquets sont découpés en « flits » qui correspondent aux plus petits éléments gérés par le réseau. Comme nous l'avons dit avant, les réseaux sur puce sont composés de routeurs, de liens et d'interfaces réseau.

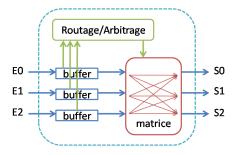

Le routeur permet l'aiguillage des paquets dans le réseau. La Figure 1.5 montre un exemple élémentaire de routeur avec une mémorisation en entrée. Il est constitué au minimum d'une matrice d'interconnexion, d'un arbitre et d'éléments de mémorisation. Les éléments de mémorisation (buffer) permettent de mémoriser les flits qui arrivent ou qui partent d'un lien physique. Il existe différentes implémentations de routeurs avec les buffers placés à l'entrée, à la sortie ou bien aux deux extrémités [21]. Nous avons choisi de nous placer, pour le reste de l'étude, dans le cas où les buffers sont à l'entrée car c'est la solution la plus simple et la plus répandue. La matrice d'interconnexion connecte toutes les entrées à toutes les sorties. Elle est contrôlée par l'arbitre qui détermine les connexions entre les entrées et les sorties. Il prend en compte la destination de chaque message et ainsi décide des connexions entrée/sortie en fonction des contentions et des priorités éventuelles.

Fig. 1.5 – Routeur élémentaire.

Le lien physique est le moyen de communiquer entre deux routeurs. Il peut être synchrone ou non et ne possède aucun élément de mémorisation. Les liens physiques peuvent être mono ou bidirectionnels.

L'interface réseau est un élément important qui permet d'isoler l'élément communiquant du réseau. De ce fait, on peut facilement connecter un nouvel élément qui n'aurait pas le même protocole de communication étant donné que ce module permet d'adapter son interface. Pour ce faire, l'interface réseau peut être vue comme la mise en cascade d'un adaptateur de protocole de communication et des fonctions usuelles des couches réseau « présentation » et « session ». Cette interface réseau peut apporter de nouvelles fonctionnalités comme la possibilité de réaliser une barrière de fréquence afin d'autoriser la multiplicité des domaines de fréquence sur une même puce.

Cette sous section a permis d'expliquer les notions. La sous section suivante va décrire les caractéristiques principales. Dans un premier temps, nous allons détailler les différents mécanismes de communication possibles.

#### 1.3.3 Les mécanismes de transport

Les mécanismes de transport correspondent à la manière dont le chemin du message est créé à travers le réseau. Ce paramètre est le premier présenté car il agit sur une grosse partie des autres paramètres. Il existe deux techniques : la commutation par circuit et la commutation par paquet.

Avec la commutation par circuit, le chemin pris par un paquet, n'est pas déterminé par le paquet lui-même mais par un contrôle distribué ou centralisé. Avec ce type de transport, le paquet est constitué exclusivement de l'information à transporter. Les chemins peuvent être déterminés statiquement ou dynamiquement. Le PicoArray de PicoChip [22] ou l'ASoC (adaptive System-On-a-Chip) du MIT [23] proposent de définir hors-ligne des séquences de chemin à travers le réseau. Ainsi dans l'ASoC, pour chaque routeur, un séquenceur vient lire dans une mémoire la configuration de la matrice d'interconnexion. Le problème de cette technique est qu'elle impose beaucoup de mémoire dans chaque routeur. De plus, le nombre de séquences est forcément borné par la taille de la mémoire ce qui limite les possibilités de reconfiguration et donc l'utilisation de l'architecture. Dans le cas du PicoArray, le changement de connexions dans la matrice du routeur est conditionné par le temps. On parle de Time Division Multiple Access (TDMA). Ceci permet de ne pas avoir à mémoriser des séquences et donc de limiter la mémoire nécessaire. Le problème de ce mécanisme provient de la réservation du chemin pour un seul utilisateur ce qui risque de contribuer à l'engorgement du réseau.

Dans tous les cas, définir les chemins statiquement implique de connaître horsligne toutes les informations concernant les communications et donc de savoir à l'avance l'application précise ce qui n'est pas possible dans le cas d'applications dynamiques. Æthereal de Philips Research [24] implémente une commutation par circuit dynamique. Lorsqu'un élément veut émettre un message vers un autre élément, il doit dans un premier temps réserver des créneaux de temps dans chaque routeur sur son chemin. Afin de créer ce chemin, un message de réservation est envoyé et alloue les créneaux dans chaque routeur. Lorsqu'un routeur répond négativement au message, le message de réservation est effacé et un message de refus est envoyé à travers le chemin déjà réservé afin d'annuler les créneaux précédemment réservés. Ce mécanisme répond à la contrainte de dynamisme des applications mais chaque communication met un temps variable pour créer le chemin, ce qui pose un problème lorsque les applications ont des contraintes temporelles. De plus, les

auteurs montrent que ce mécanisme reste coûteux au niveau surface par rapport à la communication par paquet.

Dans la communication par paquet, le chemin est décidé dynamiquement en fonction des informations contenues dans l'en-tête du paquet lorsqu'il arrive dans un routeur. Il existe trois manières principales de passer le message entre les routeurs.

La première technique, le store-and-forward est une technique dérivée des réseaux entre ordinateurs. Les paquets sont mémorisés entièrement avant d'être envoyés au routeur suivant. Ce mécanisme permet en cas de conflit entre deux paquets de mémoriser tout le paquet en un seul routeur. Cependant il est coûteux au niveau surface car chaque routeur doit être capable de mémoriser un paquet en entier sur chaque entrée. Par conséquent, cette solution n'est pas retenue dans le domaine de l'embarqué. On peut citer, tout de même, INTEL 80 Cores [25] qui implémente cette technique.

La seconde technique, le wormhole, consiste en l'envoi (le plus rapidement possible) d'un paquet par morceau à travers le réseau. Ainsi, un paquet est envoyé flit après flit à travers le réseau dès que le chemin se libère. Contrairement à la technique précédente où le paquet est mémorisé en entier dans le routeur, à tout moment, un paquet est donc réparti à travers les différents routeurs qui jalonnent son chemin. En cas de contention, le message reste distribué sur l'ensemble des routeurs du chemin. Afin de ne pas mémoriser, la destination dans chaque flit, un flit d'en-tête réserve le chemin et le flit de queue le libère. Ce mécanisme permet de diminuer le temps d'arrivée de chaque paquet mais a pour effet de surcharger le réseau en cas de contention. Cette technique est utilisée dans la majorité des NoC [26] car elle nécessite un minimum de mémoire dans chaque routeur.

La troisième technique est le Virtual-Cut-Through. Elle consiste à utiliser le wormhole mais en cas de contention, le paquet est mémorisé dans le dernier routeur. Ce mécanisme permet d'avoir les avantages des deux précédentes techniques qui sont la rapidité d'envoi et la mémorisation dans le routeur en cas de contention. Cependant il a aussi les inconvénients qui sont l'étalement du message à travers le réseau et la nécessité d'avoir des buffers capables de mémoriser un paquet en entier. Il est peu courant dans la littérature, par exemple, [27] l'utilise dans le réseau Protéo.

Nous avons dit précédemment qu'afin de trouver son chemin dans le réseau, le paquet possède un en-tête qui contient soit le chemin jusqu'à la destination, soit l'adresse de la destination. MicroSpider [28], réalisé au sein du Lab-STICC, par exemple, offre la possibilité de placer dans l'en-tête du paquet les différentes sorties que le paquet doit prendre à chaque routeur. Cela permet de connaître l'émetteur du message et ainsi éviter les attaques par faux messages sur le réseau ou des erreurs. Les trafics sont alors sécurisés étant donné que l'on peut retracer un expéditeur mais cela impose à chaque émetteur de connaître la topologie du réseau afin de générer la séquence de sortie. La deuxième solution consiste à placer dans l'en-tête l'adresse de la destination. Avec cette deuxième technique, le routeur doit déterminer vers quelle sortie, il doit acheminer le paquet en fonction de cette adresse. Deux solutions sont possibles. Dans la première solution, le routeur peut s'aider d'une table de routage comme dans [29], mais cela implique une capacité de mémorisation proportionnelle

au nombre de destinations ce qui est en opposition avec nos contraintes embarquées. La deuxième solution consiste à implémenter un algorithme de routage dans chaque routeur. Cela permet de guider dynamiquement les paquets sans avoir à mémoriser des tables de routages. Cette solution est celle retenue par la majorité des NoC car elle consomme un minimum de surface. Le paragraphe 1.3.5 va détailler ces algorithmes.

En conclusion, dans notre cas de système embarqué avec un trafic dynamique, la commutation par paquet guidée par algorithmes de routage semble être le choix le plus pertinent. En effet, cette solution permet d'accepter un trafic dynamique sur les réseaux en limitant la surface nécessaire au bon fonctionnement. Une fois le mécanisme de transport choisi, la deuxième caractéristique influente pour la suite est la topologie.

#### 1.3.4 La topologie

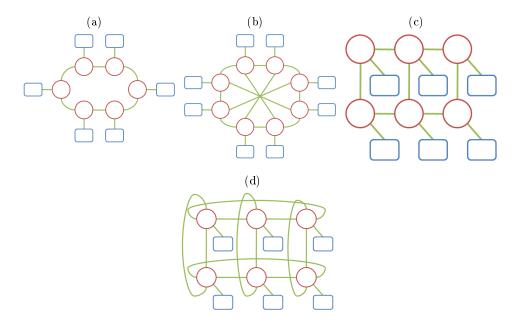

La topologie est la caractéristique qui détermine la manière dont le réseau s'organise. Il y a deux catégories de base : régulière et irrégulière qui correspondent respectivement à des topologies dont on peut extraire un motif répétitif ou non.

#### 1.3.4.1 Les topologies régulières

Les topologies régulières sont caractérisées par leurs motifs répétitifs. A l'intérieur de cette catégorie, il y a deux sous-catégories : les topologies directes et les topologies indirectes.

Les topologies directes - Une topologie est dite directe lorsque tous les routeurs sont connectés à un composant, un processeur, une mémoire ou tout autre module autre que le réseau. On différencie ces topologies en fonction du nombre d'entrée/sortie que chaque routeur possède. On trouve alors différentes topologies directes régulières possibles.

La topologie anneau comporte deux entrées/sorties en plus du lien vers le composant connecté. On peut voir sur la Figure 1.6(a) qu'un paquet ne peut transiter que de proche en proche. Cette topologie a l'avantage d'avoir un routage très simple. En effet, en fonction de la destination, il choisit de partir vers l'un de ces deux voisins. Cette simplicité implique l'unicité des chemins entre deux routeurs et un nombre important de sauts¹ dès que le nombre d'éléments à connecter augmente. Les longues distances à parcourir entraînent des latences importantes dans le réseau. De plus l'unicité du chemin impose une intolérance aux pannes et de nombreuses possibilités de contentions. Une solution simple pour repousser ces deux problèmes est de dupliquer le nombre d'anneaux entre les routeurs sur la puce. On retrouve cette solution dans le Larrabee d'Intel [30] et le CELL d'IBM [31]. Par exemple, l'EIB (Element Interconnect Bus) du CELL propose 4 bus bidirectionnels d'une largeur de 128 bits chacun.

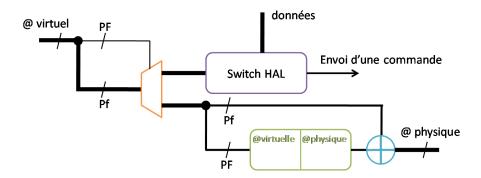

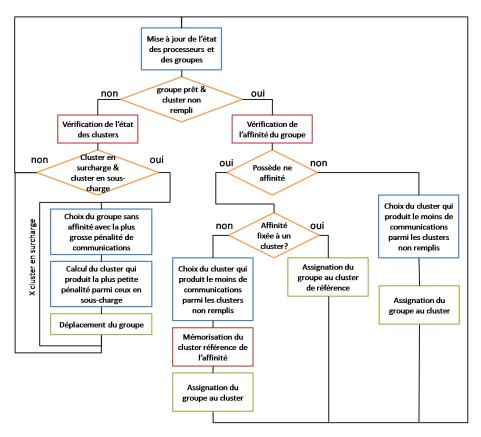

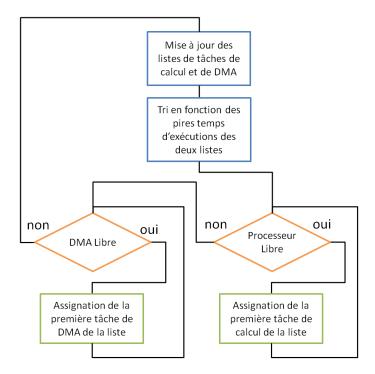

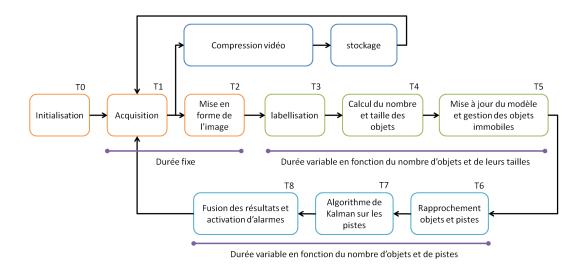

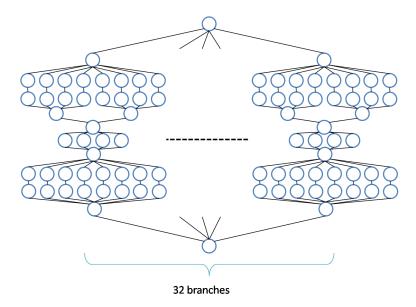

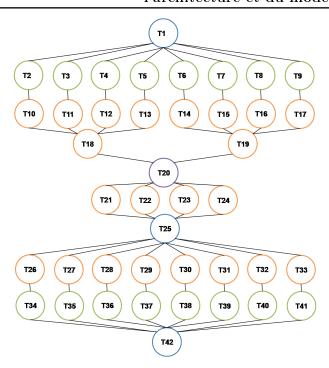

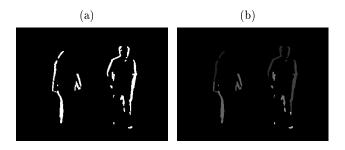

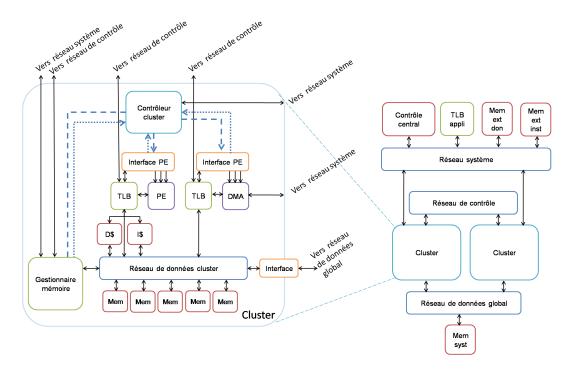

<sup>&</sup>lt;sup>1</sup>distance entre deux routeurs